Hardware Programming with Chisel #2 Hello, Chisel!

今回は前回のブログの続きとして、chiselでのFPGA開発環境の構築から実機での動作テストまで行いたいと思う。

前回のブログはこちら。

orihasam.hatenadiary.com

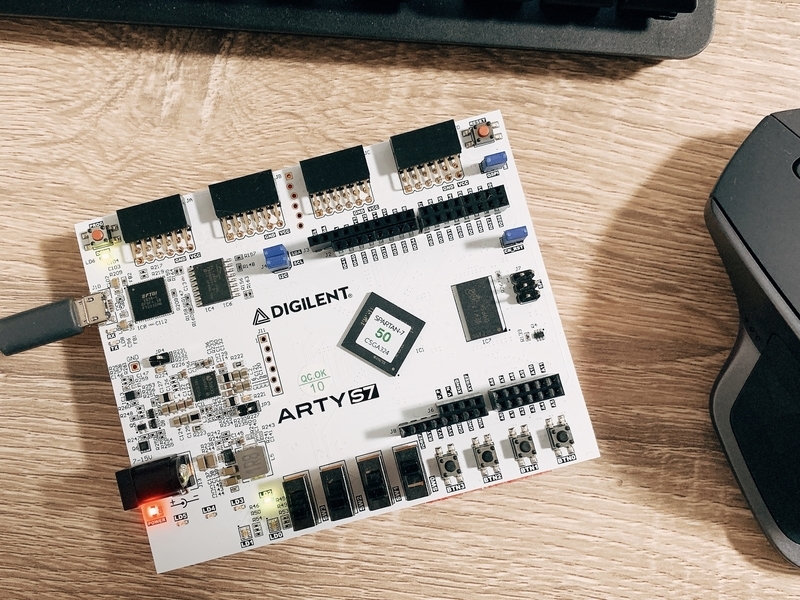

FPGA評価ボードにはXilinx社のspartan-7が搭載された、ARTY-S7を使用した。

| ザイリンクス Artix-7 35T Arty FPGA Evaluation Kit 【AES-A7MB-7A35T-G】 価格:18,392円 |

![]()

まずは、FPGAの開発環境を構築する。

verilatorのインストール

chiselで設計した回路シミュレーションを行うC++コードを出力するために、 Verilatorをインストールする。

まず、依存パッケージをインストールする。

$ sudo apt install git make autoconf g++ flex bison

次にVerilatorのgitをクローンする。

$ git clone http://git.veripool.org/git/verilator cd verilator $ git pull $ git checkout -b verilator_3_922 refsw/tags/verilator_3_922

verilatorをビルドする。

$ unset VERILATOR_ROOT $ autoconf $ ./configure $ make $ sudo make install

vivadoのインストール

chiselで開発した回路は、VerilogHDLファイルとして出力される。この回路をxilinx製のFPGAに書き込むためにvivadoというソフトウェアを用いる。

なおvivadoのインストーラの入手には、xilinx社のアカウント登録が必要である。

まず、ダウンロードしたファイルに実行権限を付与する。

$ sudo chmod +x Xilinx_Unified_2020.2_1118_1232_Lin64.bin

実行する。

$ sudo ./Xilinx_Unified_2020.2_1118_1232_Lin64.bin

GUIのインストラクションどおりにVivado HL WebPACKをインストールする。

インストール完了後、vivadoを起動するにはターミナルで以下のコマンドを入力する。

vivado

ケーブルドライバをインストール

xillinx virtual cableのドライバをインストールする。ドライバをインストールしないとFPGAに書き込むことができない。

$ cd /tools/Xilinx/Vivado/2020.2/data/xicom/cable_drivers/lin64/install_script/install_drivers $ sudo ./install_drivers

評価ボードのボードファイルをgithubリポジトリからクローンする。今回はDigilent社のArty S7-50を用いたため、Digilent社のgithubからクローンしている。

$ git clone https://github.com/Digilent/vivado-boards.git $ sudo cp -r vivado-boards/new/board_files/* /tools/Xilinx/Vivado/2020.2/data/boards/board_files

ようやく準備が整ったので、chiselプログラミングしていく。FPGAボードとして、DIGILENT社のXilinx fpga評価ボードArty-s7-50を使用する。 まずは、評価ボードに搭載されているLEDを点灯することから始める。githubリポジトリをクローンしてchiselテンプレートを入手する。

$ git clone https://github.com/ucb-bar/chisel-template.git led_on $ cd led_on $ rm -r src/main/scala/* src/test/scala/* $ rm -rf .git $ git init $ git add .gitignore * $ vim build.sbt

build.sbtを以下のように編集する。

// See README.md for license details.

ThisBuild / scalaVersion := "2.12.12"

ThisBuild / version := "1.0.0"

ThisBuild / organization := "Individual"

lazy val root = (project in file("."))

.settings(

name := "led_on",

libraryDependencies ++= Seq(

"edu.berkeley.cs" %% "chisel3" % "3.4.1",

"edu.berkeley.cs" %% "chiseltest" % "0.3.1" % "test"

),

scalacOptions ++= Seq(

"-Xsource:2.11",

"-language:reflectiveCalls",

"-deprecation",

"-feature",

"-Xcheckinit"

),

addCompilerPlugin("edu.berkeley.cs" % "chisel3-plugin" % "3.4.1" cross CrossVersio n.full),

addCompilerPlugin("org.scalamacros" % "paradise" % "2.1.1" cross CrossVersion.full )

)

chiselプログラムの作成

verilogファイルを出力するためのchiselプログラムを作成する

$ vim ./src/main/scala/led_on.scala

以下のように記述する。

// chiselパッケージをインポート

import chisel3._

// LEDを点灯するクラス

class led_on extends Module {

/** 入出力(input/output)ポートを定義

* IOにledという出力ポートを代入

*/

val io = IO(new Bundle {

//bool値を取る出力ポートを定義

val led = Output(Bool())

})

//出力ポートをtrueにする(ポートに電位差を与える)

io.led := true.B

}

//verilogファイルを作成する

object led_on extends App {

chisel3.Driver.execute(args, () => new led_on())

}

簡単にスクリプトの解説をすると、class led_on extends Module {...}で、クラスを宣言している。

val io = IO(...)では、入出力ポートを宣言している。

new Bundle {...}には、入出力信号を含むハードウェア構成を記述している。

val led = Output(Bool())は、ledと名付けられたポートがアウトプットポートであり、boolean型の信号を持つことを記述している。

:=演算子は、演算子の右側の信号によって、左側の信号が駆動されることを示している。

true.Bはtrue値をとるBooleanを意味している。

scalaプログラムを実行する。

$ sbt run

以下のようなverilogファイルが生成される。

module led_on( input clock, input reset, output io_led ); assign io_led = 1'h1; // @[led_on.scala 12:9] endmodule

FPGAへの書き込み

先程作成したverilogファイルをvivadoで読み込み、評価ボードの制約ファイルを編集することでFPGAに書き込むことができる。制約ファイルは評価ボードメーカからダウンロードできる。

今回使用したArty-s7 50の場合は、次のgithubで提供されている。

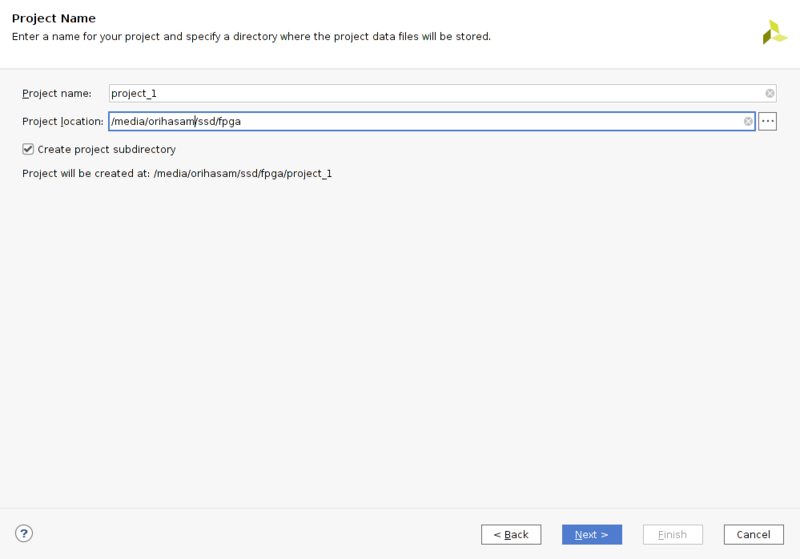

- vivadoを起動し、create projectをクリック。

- project nameとproject locationを設定する。

- RTL projectを選択してNext

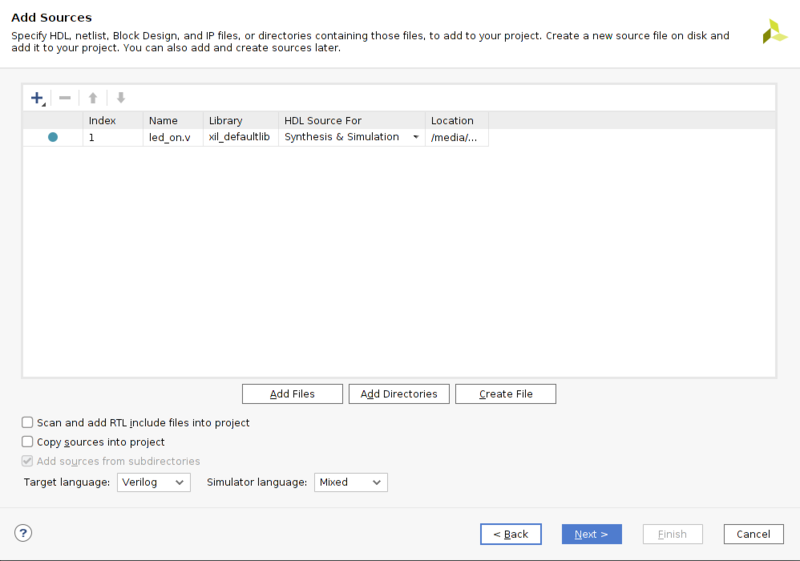

- Add Filesで先程作成したverilogファイル"led_on.v"を選択する。Target LanguageはVerilogにしておく。

- 制約ファイルを追加する。制約ファイルは、verilogファイルに合わせて編集するため、copy constraints files into projectにチェックをつけておき、元ファイルを残しておく。

- 評価ボードを選択する。

- 制約ファイルの以下の部分を編集して、led[0]をio_ledにする。

## LEDs

set_property -dict { PACKAGE_PIN E18 IOSTANDARD LVCMOS33 } [get_ports { io_led }]; #IO_L16N_T2_A27_15 Sch=led[2]

#set_property -dict { PACKAGE_PIN F13 IOSTANDARD LVCMOS33 } [get_ports { led[1] }]; #IO_L17P_T2_A26_15 Sch=led[3]

#set_property -dict { PACKAGE_PIN E13 IOSTANDARD LVCMOS33 } [get_ports { led[2] }]; #IO_L17N_T2_A25_15 Sch=led[4]

#set_property -dict { PACKAGE_PIN H15 IOSTANDARD LVCMOS33 } [get_ports { led[3] }]; #IO_L18P_T2_A24_15 Sch=led[5]

- 評価ボードをPCとUSB接続する

- 左タブのprogram and debugからopen targetを選択し、Auto connectする。

- 左タブのRun synthesisを選択し、合成を実行する。

- 合成が完了したら、そのままRun implementationにチェックを入れて実行する。

- Implementation completedダイアログが表示されたら、generate bitstreamにチェックを入れて実行する。

bitstream generation completedダイアログが表示されたらcancelをクリック。

左タブのprogram deviceをクリックし表示される"xc7s50_0"をクリックする。

bitstream fileに先程作成したbitstream fileのパスが最初から入っているのでそのままprgramボタンをクリックしてFPGAに書き込む。

FPGA評価ボードに搭載されているLEDが点灯する。

※Open Implemented Designをクリックし、Netlistタブのled_onを右クリックしてschematicを選択すると回路図が表示される。

おわりに

今回は単純にLEDを点灯するだけの回路を作成した。次回以降はより実用的な回路作成について書いていきたいと思う。

| 【送料無料】 Scalaスケーラブルプログラミング 第3版 / マーティン・オダースキー 【本】 価格:5,060円 |

![]()

| 【POD】Chiselを始めたい人に読んで欲しい本 (技術の泉シリーズ(NextPublishing)) [ 七夕 雅俊 ] 価格:2,750円 |